INC - Projekt 1 - Návrh

Obsah Dokumentu

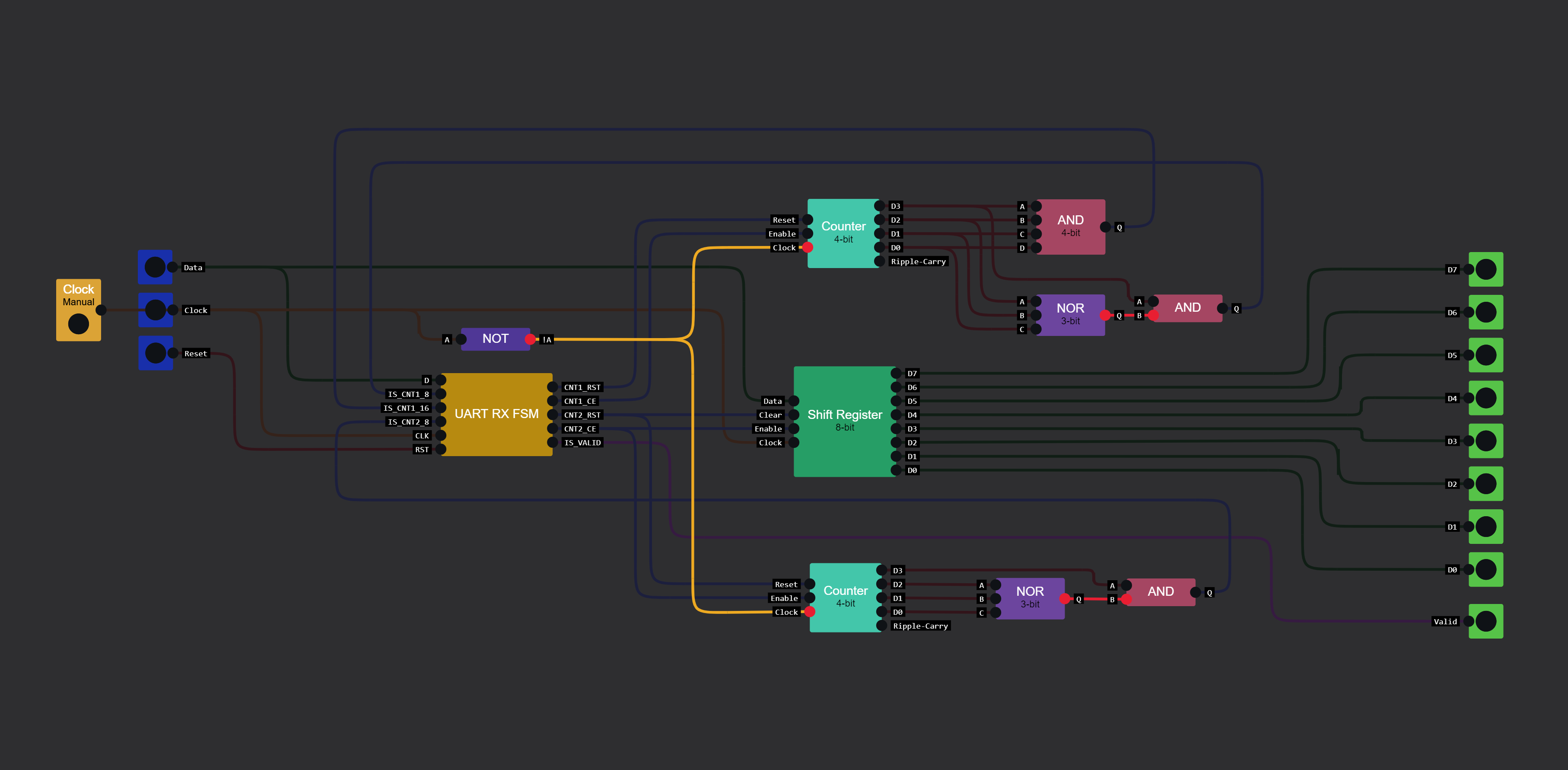

Architektúra navrhnutého obvodu (na úrovni RTL)

Schéma obvodu (outdated)

https://vut-fit.loumadev.eu/INC/projects/01/schematic.png

Poznámky

- Funkčná simulácia obvodu je dostupná na adrese: logic-constructor.loumadev.eu

- Ovládanie:

Wheel- zoomShift + LMB + Drag- navigate aroundLMB + Drag- selectionLMB select + Drag- moveLMB- interactionRMB- context menu (component, connection)

- Pre reštart (v prípade napr. chyby) stačí obnoviť stránku (

F5,Ctrl + R, refresh, ...) - Pre vytvorenie nového prázdneho projektu stačí zmeniť URL na https://logic-constructor.loumadev.eu/

Popis obvodu

Rozdelenie vodičov

- Žltá - Clock

- Zelená - Dátové linky

- Modrá - Kontrolné signály

- Fialová - Výstupné signály

- Červená - Nezaradené

Popis komponentov

- UART RX FSM - Riadiaca jednotka obvodu, slúži na ovládanie všetkých ostatných komponentov (obsahuje FSM)

- Counter 1 (horný) - Počítadlo slúžiace na počítanie cyklov pre správnu synchronizáciu

- Counter 2 (dolný) - Počítadlo slúžiace na počítanie spracovaných bitov

- Shift Register - Posuvný register slúžiaci na postupné ukladanie spracovaných bitov

- Konštrukcia NOR+AND - Kombinačný obvod na určovanie, či sa 4-bit hodnotá rovná hodnote 8 (bolo odstránené)

- Konštrukcia AND3 - Kombinačný obvod na určovanie, či sa 4-bit hodnotá rovná hodnote 15 (bolo odstránené)

Popis funkcionality

Predpoklajme, že sa obvod nachádza v počiatočnom stave, kedy je na Data pine hodnota HIGH, tj. neprechádza žiadna komunikácia. Obvod v tomto stave zotvráva, až pokiaľ sa na Data pine neobjaví hodnota LOW (start bit), kedy s nasledujúcim tickom Clocku je táto zmena detekovaná riadiacou jednotkou UART RX FSM, ktorá dáva počítadlu Counter 1 povel na počítanie. Toto počítadlo následne počíta ticky Clocku a zároveň kombinačná logika porovnáva aktuálnu hodnotu počítadla. Ak počítadlo dosiahne hodnotu 6 (*1), riadiaca jednotka prepne svoj vnútorný stav na prijímanie. Táto operácia mala za následok, že obvod efektívne preskočil prvých 8 tickov Clocku.

Pri zmene stavu na prijímanie, riadiaca jednotka vysiela signál na zresetovanie počítadla Counter 1 na 0. V momente, ak počítadlo Counter 1 dosiahne hodnotu 14 (*1), riadiacia jednotka, pri ďalšom ticku Clocku vysiela signál CNT1_RST na zresetovanie počítadla Counter 1 a signál CNT2_CE na spustenie počítania počítadla Counter 2. V nasledujúcom ticku Clocku sa Counter 1 zresetuje na 0, Counter 2 bude obsahovať hodnotu o 1 väčšiu ako obsahoval. Keďže Counter 1 už neobsahuje hodnotu 14, riadiaca jednotka prestane vysielať signál CNT2_CE, vďaka čomu pri nasledujúcom ticku Clocku, počítadlo Counter 2 nebude počítať. Ak počítadlo Counter 2 neobsahuje hodnotu 8, zároveň sa vysiela aj signál SHREG_CE, ktorý je priamo spojený s vstupom Enable posuvného registra Shift Register, aktuálna hodnota na pine Data sa teda vloží do tohto registra. Touto operáciou bolo efektívne preskočených 16 tickov Clocku a prebehla observácia dát na Data pine, ktoré sa uložili do posuvného registra Shift Register.

Táto operácia sa opakuje v slučke, až pokiaľ počítadlo Counter 2 nedosiahne hodnotu 8. V tom momente sa prestance vysielať signál SHREG_CE, čo má za následok, že nasledujúce dáta nebudú uložené. Po prebehnutí 16 tickov Clocku, kedy by malo dôjsť k observácii dát, sa riadiaca jednotka pozrie na aktuálnu hodnotu pinu Data, či je HIGH, čo znamená, že bol prijatý stop bit. Riadiaca jednotka následne vysiela signál IS_VALID, ktorý je priamo pripojený na výstupný pin Valid. Ak je hodnota LOW, čo znamená, že prichádzajúce dáta mohli byť poškodené, riadiaca jednotka signál IS_VALID nevysiela. Následne riadiaca jednotka prechádza do počiatočného stavu a vysielaním signálov CNT1_RST a CNT2_RST resetuje počítadlá.

- *1 - od nuly,

-1(synchrónny reset + update druhého countru)

Návrh automatu (Finite State Machine)

Schéma automatu

Zoznam stavov a signálov

- Stavy automatu:

IDLE,WAIT,RECEIVE - Vstupné signály:

D,CNT1,CNT2 - Výstupné signály (Mealy):

CNT1_CE,CNT1_RST,CNT2_CE,CNT2_RST,SHREG_CE,IS_VALID - Výstupné signály (Moore): none

Implicitné hodnoty

- Výstupy: Všetky výstupné signály sú implicitne

LOW(0) - Podmienky: Všetky signály sú implicitne

X(don't care)

https://vut-fit.loumadev.eu/INC/projects/01/fsm.svg

Popis funkcionality

Podrobný popis fungovania stavového automatu je popísaný v časti Popis funkcionality, v sekcii Architektúra navrhnutého obvodu ako riadiaca jednotka.

Automat funguje na princípe, že na začiatku komunikácie sa počká 8 tickov clocku a následne sa každý 16-tý tick observujú dáta. Počkaním 8 tickov sa observácia posunie o 8 tickov clocku, čo je práve polovica 16 (stanovený počet tickov clocku pre jeden bit), čím sa dosiahne observácia presne v strede prenášaného bitu.

Automat sa iniciálne nachádza v stave IDLE, kedy sú obe počítadlá zresetované (nastavené na hodnotu 0). Počas tohto stavu automat čaká na start bit (hodnotu LOW na D pine). Po prijatí start bitu sa automat dostane do stavu WAIT, kde sa čaká 8 tickov (vytvorí sa tak offset do polovice času observácie). Po dosiahnutí 8 tickov sa automat dostane do stavu RECEIVE, kde v cykle pushuje jednotlivé prijaté bity do posuvného registra. Po prijatí 8 bitu sa daný byte zvaliduje kontrolou s D pinom. Výsledok tejto validácie je potom viditeľný na výstupnom pine IS_VALID.

https://vut-fit.loumadev.eu/INC/projects/01/design.md

Návrh číslicových systémů (INC 22/23L)

Jaroslav Louma (xlouma00)

10. Marec 2023 (C)